You have Downloaded, yet Another Great Resource to assist you with your Studies ©

Thank You for Supporting SA Exam Papers

Your Leading Past Year Exam Paper Resource Portal

Visit us @ www.saexampapers.co.za

# basic education

Department:

Basic Education

REPUBLIC OF SOUTH AFRICA

# NATIONAL SENIOR CERTIFICATE

**GRADE 12**

**ELECTRICAL TECHNOLOGY: ELECTRONICS**

**NOVEMBER 2024**

**MARKING GUIDELINES**

**MARKS: 200**

These marking guidelines consist of 16 pages.

NSC – Marking Guidelines

DBE/November 2024

#### INSTRUCTIONS TO THE MARKERS

- 1. All questions with multiple answers imply that any relevant, acceptable answer should be considered.

- 2. Calculations:

- 2.1 All calculations must show the formulae.

- 2.2 Substitution of values must be done correctly.

- 2.3 All answers MUST contain the correct unit to be considered.

- 2.4 Alternative methods must be considered, provided that the correct answer is obtained.

- 2.5 Where an incorrect answer could be carried over to the next step, the first answer will be deemed incorrect. However, should the incorrect answer be carried over correctly, the marker has to recalculate the values, using the incorrect answer from the first calculation. If correctly used, the candidate should receive the full marks for subsequent calculations.

- 3. These marking guidelines is only a guide with model answers. Alternative interpretations must be considered and marked on merit. However, this principle should be applied consistently throughout the marking session at ALL marking centres.

NSC – Marking Guidelines

DBE/November 2024

# **QUESTION 1: MULTIPLE CHOICE**

| 1.1 | B✓ |  |

|-----|----|--|

| 4.0 |    |  |

1.3 B

$$\checkmark$$

(1)

$$1.10 C \checkmark (1)$$

(1)

4 NSC – Marking Guidelines DBE/November 2024

#### **QUESTION 2: OCCUPATIONAL HEALTH AND SAFETY**

- 2.1 Workplace means any premises or place where a person performs work ✓ in the course of employment. ✓ (2)

- 2.2 Your right to fair labour practices. ✓

Your right to work reasonable hours. ✓

Your right to belong to a trade union.

Your right to earn a living wage.

Your right not to be discriminated against.

Your right to work in a safe environment.

(2)

2.3 Poor ventilation reduces the correct amount of oxygen ✓ which might lead to drowsiness. ✓

NOTE: If reference is made to other effects that relates to poor ventilation like drowsiness, accidents etc. the answer will be accepted on merit.

(2)

- 2.4 To dismiss an employee without due process. ✓

- To reduce the rate of remuneration without due process. ✓

- Alter the terms of conditions of his/her employment to terms of conditions that is less favourable to him/herself.

- Harassment and verbal abuse.

- Alter position relative to other people.

- Treat employees unfair because of race.

NOTE: If a learner only mentions an infringement of rights only 1 mark will be awarded. Duplicate mentioning of rights will not be awarded.

(2)

2.5 Equipment may be damaged making it unsafe ✓ endangering the life of other users ✓ which might lead to an accident/injury.

(2) **[10]**

NSC – Marking Guidelines

DBE/November 2024

(2)

### **QUESTION 3: RLC CIRCUITS**

- 3.1 3.1.1 Inductive reactance is the opposition to the flow of current ✓ when an inductor is connected to an ac supply. ✓ Inductive reactance is the opposition offered to the flow of alternating current by an inductor. (2)

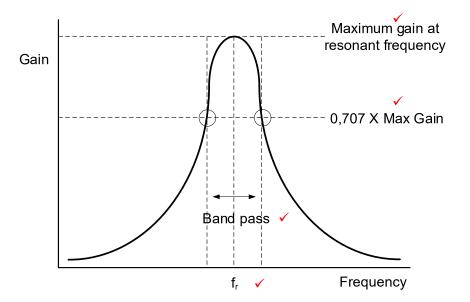

- 3.1.2 Bandwidth is the range of frequencies ✓ for which the circuit output voltage (or) current value equals 70,7 % or more of its maximum amplitude. ✓

NOTE: A band of frequencies centred around the resonant frequency without mentioning 70,7% of the amplitude will be awarded 1 mark.

The bandwidth of an RLC circuit refers to the range of frequencies over which an RLC circuit effectively responds to an input signal and transmits more than 50% of the power to a load.

- 3.2 3.2.1 Lagging ✓ (1)

- 3.2.2  $V_L = IX_L$   $I = \frac{V_L}{X_L}$   $= \frac{3,45}{150}$  = 23 mA = 0,023 A(3)

- 3.2.3  $X_{L} = 2\pi f L$   $L = \frac{X_{L}}{2\pi f}$   $= \frac{150}{2\pi (50)}$

$$= 477,46 \, mH = 0,48 \, H$$

(3)

3.2.4  $Z = \sqrt{R^2 + (X_L - X_C)^2}$   $R = \sqrt{Z^2 - (X_L - X_C)^2}$   $= \sqrt{106,42^2 - (150 - 113,6)^2}$   $= 100 \Omega$ (3)

$= 100 \Omega$   $V_{L}$   $(V_{L} - V_{C})$   $\theta$

V<sub>c</sub>♥ ✓

NOTE: Rotation and V<sub>T</sub> are compulsory marks, thereafter any two correctly placed labels.

X<sub>L</sub> and X<sub>C</sub> will not be accepted as the given diagram to complete from the question paper indicated voltage values. (4)

Rotation

Copyright reserved

6 NSC – Marking Guidelines DBE/November 2024

(3)

(3)

(3) **[35]**

3.2.6 A decrease in frequency caused the inductive reactance to decrease ✓ and the capacitive reactance to increase. ✓ When these two values move closer to one another their effects cancel each other out decreasing the impedance ✓ causing the current to increase and the phase angle to decrease.

$3.3 3.3.1 I_R = \frac{V_T}{R}$

$=\frac{230}{60}$

= 3,83 *A* ✓

$3.3.2 X_C = \frac{V_T}{I_C}$

<del>230</del> <del>9</del>,2

$= 25 \Omega \tag{3}$

3.3.3  $I_T = I_R = 3,83 \text{ A}$

$X_C = X_L$  which indicates that the circuit is at resonance

is at resonance (2)

3.3.4  $X_C = X_L$   $Q = \frac{R}{X_L}$

$=\frac{60}{25}$

$= 2,4 \tag{3}$

$3.3.5 BW = \frac{f_r}{Q}$

50 2.4

= 20,83 Hz

NSC – Marking Guidelines

DBE/November 2024

## **QUESTION 4: SEMICONDUCTOR DEVICES**

| 4.1 | P-chann | nel ✓ enhancement ✓ MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 4.2 | 4.2.1   | The pinching state is reached by increasing the gate to source voltage, ✓ which widens the depletion regions on both sides of the channel, ✓ resulting in the drain current (I <sub>D</sub> ) being reduced. ✓                                                                                                                                                                                                                                    | (3) |  |

|     | 4.2.2   | The Junction field effect transistor (JFET) operates with its gate-<br>source junction ✓ reverse—biased ✓ which makes the input<br>resistance at the gate very high whilst the bipolar junction transistor<br>operates with the forward biased base-emitter junction ✓ which<br>result in a lower resistance.                                                                                                                                     | (3) |  |

| 4.3 | 4.3.1   | MOSFET transfer ✓ characteristic curve MOSFET transconductance characteristic curve                                                                                                                                                                                                                                                                                                                                                               | (1) |  |

|     | 4.3.2   | A – Cut-off region ✓<br>B – Enhancement region ✓                                                                                                                                                                                                                                                                                                                                                                                                  | (2) |  |

|     | 4.3.3   | <ul> <li>When the input gate-source voltage (V<sub>GS</sub>) is low√, the channel drain current (I<sub>D</sub>) is low. ✓</li> <li>When the gate-source voltage rises, ✓ the channel widens and the drain current increases. ✓</li> <li>NOTE: If a candidate mentions that V<sub>GS</sub> and I<sub>D</sub> are directly proportional 2 marks will be awarded and any of the two bullets above can be mentioned for the other 2 marks.</li> </ul> | (4) |  |

|     | 4.3.4   | Amplifier ✓<br>Switch ✓                                                                                                                                                                                                                                                                                                                                                                                                                           | (2) |  |

| 4.4 |         | FET only operates in the depletion mode. ✓<br>IOSFET operates in both depletion and enhancement modes.                                                                                                                                                                                                                                                                                                                                            |     |  |

| 4.5 | 4.5.1   | Positive pulse. ✓                                                                                                                                                                                                                                                                                                                                                                                                                                 | (1) |  |

|     | 4.5.2   | When the emitter is supplied with sufficient current, $\checkmark$ the operating point will continue falling $\checkmark$ from the peak point until it reaches the valley point. When $V_E \geq V_X$ , the operating point will fall from the peak point until it reaches the valley point.                                                                                                                                                       |     |  |

|     | 4.5.3   | (a) Unijunction transistor (UJT) consists of a single PN -junction ✓<br>whilst a bipolar junction transistor (BJT) consists of two<br>PN-junctions ✓ called Emitter Base Junction and Collector-<br>Base junction.                                                                                                                                                                                                                                | (2) |  |

|     |         | (b) The unijunction transistor is essentially a voltage controlled switch and does not have amplifying properties. ✓ The Bipolar Junction transistor (BJT) is current operating device                                                                                                                                                                                                                                                            |     |  |

and has amplifying properties. ✓

(2)

8 NSC – Marking Guidelines DBE/November 2024

4.6 4.6.1 FIGURE A - output voltage will be positive/high. ✓

FIGURE B - output voltage will be negative/low. ✓ (2)

4.6.2 Small size ✓ Cheap ✓

Low power consumption

Highly stable

Highly reliable (2)

4.6.3 Common mode rejection ratio is the ability of an op-amp to suppress common mode signals. ✓

The common mode rejection ratio is the ratio between the output voltage to the common input voltage when the same signal is applied simultaneously to both inputs. (1)

4.7 4.7.1 Negative feedback. ✓ (1)

4.7.2  $A_V = -\frac{R_F}{R_{IN}}$   $= -\frac{4700}{470}$  = -10(3)

4.7.3  $V_{OUT} = A_V \times V_{IN}$   $V_{OUT} = V_{IN} \times \left(-\frac{R_f}{R_{IN}}\right)$   $V_{OUT} = V_{IN} \times \left(-\frac{R_f}{R_{IN}}\right)$   $V_{OUT} = 0.002 \times \left(-\frac{4700}{470}\right)$   $V_{OUT} = -0.02 V$  (3)

- 4.7.4 The output voltage will be able to swing above ✓ and below ✓ the zero levels. (2)

- 4.8.1 Controlling the positioning of a servo device. ✓

Temperature measurement.

Timers in oven temperature control.

Oscillator as motor speed control. (1)

- 4.8.2 The NPN transistor (T<sub>1</sub>) will only turn on when output  $\bar{Q}$  from the flip-flop goes high.  $\checkmark$  (1)

- 4.8.3 When the inverting terminal voltage is higher the comparator's output will be low. ✓ (1)

- 4.8.4 It divides the supply voltage into three equal values. ✓

The resistors act as voltage dividers. (1)

Electrical Technology: Electronics 9 DBE/November 2024

NSC – Marking Guidelines

4.8.5 The 555 IC will be triggered ✓ and the output voltage at Pin 3 rises near to the supply voltage ✓ NOTE: Due to the error in the schematic diagram of the 555 IC, the following response will be accepted:

When pin 2 falls below ½Vcc, the output of comparator C<sub>2</sub> will be low, if R of the flip-flop is high, the circuit will be reset, if R is low, the circuit will stay in its previous state.

(2) **[45]**

# **QUESTION 5: SWITCHING CIRCUITS**

| QUESTION 5: SWITCHING CIRCUITS |   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                              |     |  |

|--------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 5.                             | 1 | Negative feedback is when a portion of the output signal $\checkmark$ is fed back to the input, out of phase $\checkmark$ or subtracted from the input. |                                                                                                                                                                                                                                                                                                                                              |     |  |

| 5.:                            | 2 | 5.2.1                                                                                                                                                   | Schmitt trigger ✓                                                                                                                                                                                                                                                                                                                            | (1) |  |

|                                |   | 5.2.2                                                                                                                                                   | Bistable multivibrator ✓                                                                                                                                                                                                                                                                                                                     | (1) |  |

|                                |   | 5.2.3                                                                                                                                                   | Monostable multivibrator ✓                                                                                                                                                                                                                                                                                                                   | (1) |  |

| 5.                             | 3 | 5.3.1                                                                                                                                                   | R₂ is a pull-up resistor ✓<br>R₂ keeps the voltage on pin 2 high.                                                                                                                                                                                                                                                                            | (1) |  |

|                                |   | 5.3.2                                                                                                                                                   | <ul> <li>When S₂ is pressed it connects pin 2 to 0 V. ✓</li> <li>This low input triggers the circuit and the output goes high. ✓</li> <li>When output goes high LED₂ is forward biased and switched ON. ✓</li> <li>while LED₁ is reversed biased and switched OFF. ✓</li> </ul>                                                              | (4) |  |

|                                |   | 5.3.3                                                                                                                                                   | The circuit is reset by pressing $S_1$ . $\checkmark$ This connects reset pin 4 to 0 V. $\checkmark$                                                                                                                                                                                                                                         | (2) |  |

| 5.                             | 4 | 5.4.1                                                                                                                                                   | 0 V <b>✓</b>                                                                                                                                                                                                                                                                                                                                 | (1) |  |

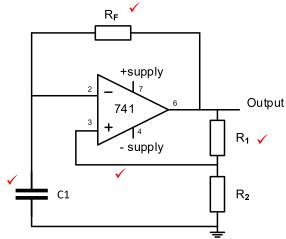

|                                |   | 5.4.2                                                                                                                                                   | During its natural resting condition, the negative reference voltage keeps the potential on the inverting input negative ✓ ensuring that the output remains stable at +Vcc. ✓                                                                                                                                                                | (2) |  |

|                                |   | 5.4.3                                                                                                                                                   | When a positive trigger voltage greater than V <sub>REF</sub> is applied to the inverting input its potential will be greater than the 0 V on the non-inverting input ✓ causing the output to saturate to − V <sub>CC</sub> ✓ where it will remain for the duration of the time constant determined by C <sub>2</sub> and R <sub>2</sub> . ✓ | (3) |  |

NSC - Marking Guidelines

DBE/November 2024

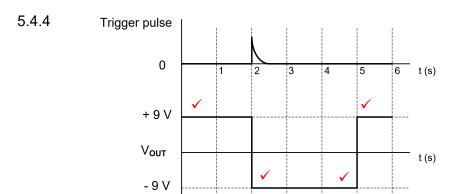

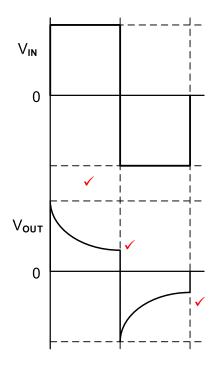

NOTE: 1 mark for starting the output at +9 V

1 mark for the output changing from +9 V to -9 V at trigger input

1 mark for the correct duration of the output state

1 mark for the return to +9 V (4)

An inverted waveform will loose 1 mark for orientation.

5.5 5.5.1

(4) 5.5.2 The output voltage of a 741 op-amp astable multivibrator circuit constantly changes between + Vcc and -Vcc ✓ where the output of

a 555 IC astable multivibrator circuit changes between +Vcc

and 0 V. ✓

Variable resistor/Potentiometer R₂ ✓ (1)

5.6.2 Resistor R₁ ✓ Thermistor ✓ (2)

5.6.3 By adjusting variable resistor R₂ ✓ the new reference voltage at the inverting input will change. < (2)

5.7 Clean up signals in radio receivers. ✓

Eliminate noise caused by switch bounce in digital circuits. <

Changing of sine waves into square or rectangular waves

Signal recovery after severe distortion.

SA EXAM PAPERS

5.6

5.6.1

(2)

(2)

NSC – Marking Guidelines

DBE/November 2024

- 5.8 Variable resistor R₄ provides negative feedback ✓ that controls the gain of the circuit. ✓ (2)

- 5.8.2  $V_{OUT} = -\left(V_1 \frac{R_F}{R_1} + V_2 \frac{R_F}{R_2} + V_3 \frac{R_F}{R_3}\right)$   $= -\left(0.5 \times \frac{72000}{10000} + 0.45 \times \frac{72000}{10000} + 0.3 \times \frac{72000}{10000}\right)$  = -9 V(3)

NOTE: Due to the error on the formula sheet provided, the following calculation will be accepted.

$$V_{OUT} = -\left(V_1 \frac{R_F}{R_1} + V_1 \frac{R_F}{R_2} + V_1 \frac{R_F}{R_3}\right)$$

$$= -\left(0.5 \times \frac{72000}{10000} + 0.5 \times \frac{72000}{10000} + 0.5 \times \frac{72000}{10000}\right)$$

$$= -10.8 V$$

- 5.8.3 When  $R_F = R_1 = R_2 = R_3$ . ✓ They cancel each other out in the formula giving  $V_{0UT} = -(V_1+V_2+V_3)$ .

When  $R_4$  is set to 10 kΩ the overall circuit gain is 1. (1)

- 5.8.4 When R₄ is increased beyond 72 kΩ the gain of the amplifier increases ✓ driving it into saturation and causing distortion on the output. ✓

NOTE: Because of the formula provided on the formula sheet a reason in-line with the calculated answer in 5.8.2 will be accepted. e.g. The circuit is already in saturation, when R₄ is increased the output voltage will remain at a maximum of 9 V. (2)

- 5.9 5.9.1 A passive differentiator primarily performs mathematical differentiation on an input signal, ✓ producing an output voltage proportional to the rate of change of the input voltage. ✓ (2)

12 NSC – Marking Guidelines DBE/November 2024

5.9.2

NOTE: The wave shape must be correct before any marks are allocated

1 mark for orientation

1 mark for each ½ cycle

(3)

5.10 In an op-amp differentiator a capacitor is connected to the inverting input and resistor used in the feedback loop. ✓

In an op-amp integrator a resistor is connected to the inverting input with a capacitor in the feedback loop. ✓

(2)

[50]

13 NSC – Marking Guidelines DBE/November 2024

(2)

(2)

(1)

(2)

#### **QUESTION 6: AMPLIFIERS**

6.1 Attenuation refers to a circuit with a output voltage smaller ✓ than the input voltage. ✓

Attenuation is the reduction in signal voltage as it passes through a circuit and corresponds to a gain of less than 1.

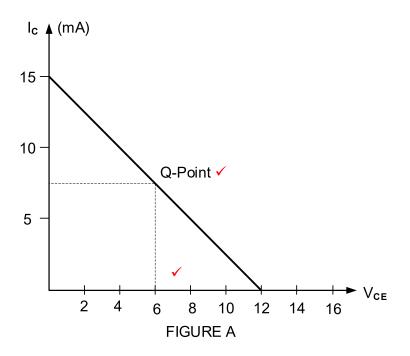

- 6.2 6.2.1 DC load line is the line on the output characteristic of a transistor circuit showing the operating points of the amplifier. ✓ (1)

- 6.2.2 VcE will be equals to Vcc =  $12 \text{ V.}\checkmark$  (1)

- 6.2.3 For class A amplification, the quiescent voltage is 6 V. ✓

The value of the quiescent voltage is half ✓ the value of the supply voltage i.e ½ Vcc. (2)

6.2.4

- 6.3 6.3.1 RC coupled amplifier. ✓

- 6.3.2 Roll-off is the rate at which the gain decreases at high frequencies. ✓ (1)

- 6.3.3 (a) At high frequencies, the reactance of the small parasitic capacitances of the transistors ✓ becomes lower ✓ and lower, reducing the gain. (2)

- (b) At low frequencies the coupling capacitor's reactance rises, ✓ blocking more of the signal ✓ and also the reactance of the decoupling capacitors with the emitter resistance limit the gain.

SA EXAM PAPERS

Electrical Technology: Electronics DBE/November 2024 NSC - Marking Guidelines 6.4 6.4.1 Transformer coupled ✓ amplifier. (1) 6.4.2 AC relay ✓ AC motor ✓ Piezo Buzzer (2)6.4.3 To match the two impedances and separate the dc circuits. To couple the output of Q<sub>1</sub> to the input of Q<sub>2</sub>. (1) 6.4.4 There would be no maximum power transfer to the loudspeaker ✓ because the output impedance of the amplifier ✓ does not match with the input impedance of the speaker ✓ thus meaning the output sound will be softer. (3) 6.5 6.5.1 Complementary ✓ Push pull amplifier. (1)

6.5.2 Block DC signals ✓ and allows the AC signals to pass through. ✓

The capacitor couples the circuit with the speaker and acts as a short term power source for the PNP transistor during each negative half cycle. (2)

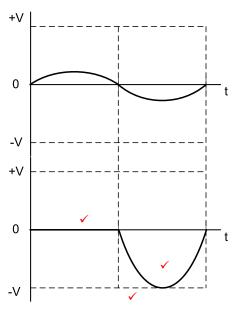

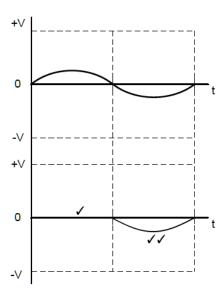

6.5.3

(3)

NOTE: 1 mark for each half cycle = 2 1 mark for amplification

15 NSC – Marking Guidelines DBE/November 2024

NOTE: 1 mark for same phase on negative half-cycle 1 mark for NO amplification shown.

6.6 The purpose of transistor Q₁ is to amplify the input signal to a value that drives the tank circuit to oscillation. ✓

(1)

6.6.2 By varying capacitors C₁ and C₂, the tuned circuit will resonate at different frequencies, ✓ therefore changing range of frequencies. ✓

(2)

6.6.3

6.7 6.7.1 The transistor will be driven alternately on and off, ✓ which in turn continually charges the tank circuit ✓ keeping it oscillating at a constant ✓ amplitude.

(3)

(4)

- Block dc current from passing ✓ and allow the AC signal to pass. ✓

- The coupling capacitors C<sub>2</sub> and C<sub>3</sub> only allows a Radio frequency signal from the amplifier to the tank circuit and back.

(2)

SA EXAM PAPERS

| Electrical Technology |                                                                                                                          | 6<br>ng Guidelines  | DBE/November 2024                   |                    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------|--------------------|

| 6.8 6.8.1             | The values of the capacite selected in such a way to phase shift of 60°. ✓                                               | ,                   |                                     | (2)                |

| 6.8.2                 | RC phase-shift oscillator a desired frequency frequencies.  The RC phase-shift osci rely on resonant/phase strequencies. | ✓ and blocks/suppre | sses all other<br>cy amplifier both | (2)                |

| the feedb             | e shift oscillators use resiseack network. ✓<br>eator uses capacitors and in                                             |                     | ,                                   | (2)<br><b>[45]</b> |

|                       |                                                                                                                          |                     | TOTAL:                              | 200                |